一、 引言:芯片時(shí)代的基石

在現(xiàn)代信息社會(huì)的核心,納米集成電路(IC)扮演著無(wú)可替代的角色。它不僅是智能手機(jī)、計(jì)算機(jī)和各類智能設(shè)備的“大腦”,更是推動(dòng)人工智能、物聯(lián)網(wǎng)和5G通信等技術(shù)發(fā)展的物理基礎(chǔ)。集成電路制造是一項(xiàng)極度精密和復(fù)雜的系統(tǒng)工程,其核心在于將數(shù)億乃至數(shù)百億個(gè)晶體管及其他電子元件,集成在指甲蓋大小的硅片上。本文將系統(tǒng)性地闡述納米級(jí)CMOS邏輯電路與存儲(chǔ)器的制造流程,并探討其如何通過計(jì)算機(jī)系統(tǒng)集成與綜合布線,最終構(gòu)成功能完備的電子設(shè)備。

二、 納米集成電路制造工藝概述

納米集成電路制造,通常指特征尺寸在納米級(jí)別(如7nm、5nm、3nm)的超大規(guī)模集成電路(VLSI)制造技術(shù)。整個(gè)制造過程在超凈間內(nèi)進(jìn)行,涉及數(shù)百道精密工序,主要包括以下幾個(gè)核心階段:

- 晶圓制備:以高純度單晶硅柱為基礎(chǔ),切割成厚度不足1毫米的圓形薄片,稱為晶圓(Wafer),作為所有電路的物理載體。

- 前道工藝(FEOL):在晶圓上制造晶體管等基本元件的階段。這是最核心、技術(shù)難度最高的部分。

- 后道工藝(BEOL):在晶體管之上,構(gòu)建多層金屬互連線路,將各個(gè)晶體管連接成完整電路的階段。

- 測(cè)試與封裝:對(duì)制造完成的芯片進(jìn)行功能與性能測(cè)試,然后進(jìn)行切割、封裝,形成可安裝的獨(dú)立芯片。

三、 CMOS邏輯電路制造流程詳解

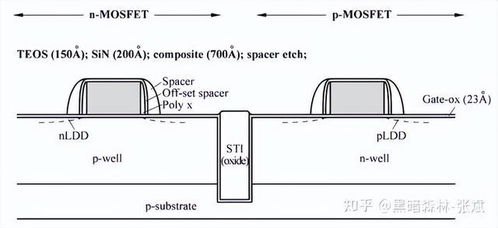

CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)技術(shù)是當(dāng)今邏輯集成電路(如CPU、GPU)的絕對(duì)主流,因其低功耗、高集成度等優(yōu)點(diǎn)而被廣泛采用。其核心是制造出NMOS和PMOS兩種互補(bǔ)的晶體管。

核心步驟包括:

- 隔離與阱區(qū)形成:通過氧化和光刻技術(shù)在晶圓上定義出不同的活性區(qū)域,并通過離子注入工藝形成P型阱和N型阱,為NMOS和PMOS晶體管準(zhǔn)備各自的“地基”。

- 柵極結(jié)構(gòu)形成(關(guān)鍵技術(shù)節(jié)點(diǎn)):

- 生長(zhǎng)超薄(僅幾個(gè)原子層厚度)的高質(zhì)量柵極氧化層(介電質(zhì))。

- 沉積多晶硅或金屬作為柵極材料。

- 利用極紫外(EUV)光刻等先進(jìn)技術(shù),將設(shè)計(jì)好的電路圖形精確轉(zhuǎn)移到晶圓上,并通過刻蝕形成納米尺度的柵極結(jié)構(gòu)。柵極的長(zhǎng)度即代表了工藝的“納米”數(shù)(如3nm)。

- 源漏區(qū)形成:在柵極兩側(cè),通過離子注入高濃度雜質(zhì),形成晶體管的源極和漏極。對(duì)于先進(jìn)工藝,常采用嵌入式硅鍺(eSiGe)或碳化硅(SiC)等應(yīng)變工程技術(shù)來提升載流子遷移率,從而提高晶體管性能。

- 接觸孔與局部互連:在晶體管制造完成后,沉積絕緣層,并蝕刻出接觸孔,填充鎢等金屬,形成與晶體管源、漏、柵極的電學(xué)連接。

四、 存儲(chǔ)器制造流程簡(jiǎn)介(以DRAM和3D NAND為例)

存儲(chǔ)器芯片的制造邏輯與CMOS邏輯電路有共通之處,但在結(jié)構(gòu)上追求更高的密度。

- DRAM(動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器):核心是制造一個(gè)晶體管加一個(gè)電容(1T1C)的存儲(chǔ)單元。其挑戰(zhàn)在于在極小面積內(nèi)制造出容量足夠、漏電小的立體電容,這需要復(fù)雜的刻蝕和材料沉積技術(shù)來構(gòu)建圓柱狀或溝槽狀電容。

- 3D NAND Flash(三維閃存):這是當(dāng)前大容量存儲(chǔ)的主流技術(shù)。其工藝核心是“堆疊”。先在晶圓上交替沉積數(shù)十甚至上百層的絕緣層和柵極材料(如多晶硅),形成像千層糕一樣的結(jié)構(gòu)。然后,通過高深寬比的垂直通道刻蝕技術(shù),從上到下打穿所有層,并在通道中填充存儲(chǔ)材料(電荷陷阱層)和溝道材料,最終形成垂直串起的存儲(chǔ)單元串。這種結(jié)構(gòu)極大提升了單位面積的存儲(chǔ)密度。

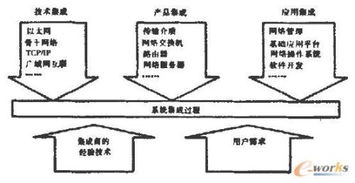

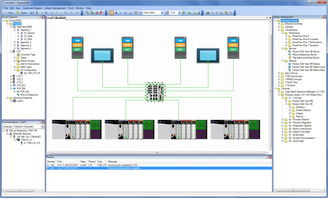

五、 從芯片到系統(tǒng):計(jì)算機(jī)系統(tǒng)集成與綜合布線

制造出的芯片是功能的載體,但必須通過系統(tǒng)集成才能發(fā)揮其作用。這包含硬件和物理連接兩個(gè)層面。

- 硬件系統(tǒng)集成:

- 芯片級(jí)封裝(Chiplet):先進(jìn)集成方式,將不同工藝、不同功能的裸芯片(如CPU、I/O、存儲(chǔ)器)通過硅中介層或先進(jìn)封裝技術(shù)(如2.5D/3D封裝)集成在一個(gè)封裝內(nèi),實(shí)現(xiàn)高性能、高帶寬互聯(lián),是超越摩爾定律的重要路徑。

- 板級(jí)集成:將封裝好的芯片與其他分立元件(電阻、電容等)一起,安裝到印刷電路板(PCB)上。主板的設(shè)計(jì)需要綜合考慮電源分配、信號(hào)完整性、熱管理和電磁兼容性。

- 整機(jī)集成:將主板、電源、存儲(chǔ)設(shè)備、散熱系統(tǒng)等組裝成完整的計(jì)算機(jī)或服務(wù)器。

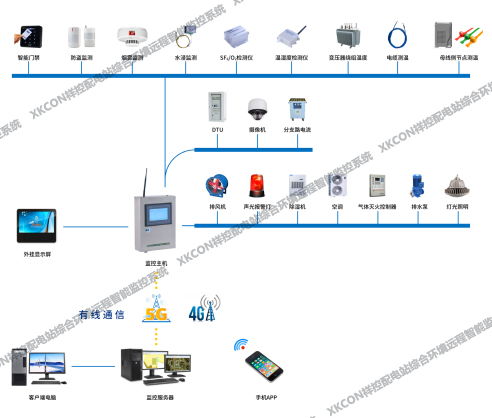

- 綜合布線:

- 在芯片設(shè)計(jì)階段,電子設(shè)計(jì)自動(dòng)化(EDA)工具中的“綜合”與“布線”環(huán)節(jié),決定了晶體管之間數(shù)以億計(jì)的信號(hào)連接如何在有限的金屬層內(nèi)最優(yōu)實(shí)現(xiàn),確保時(shí)序正確、信號(hào)無(wú)干擾。

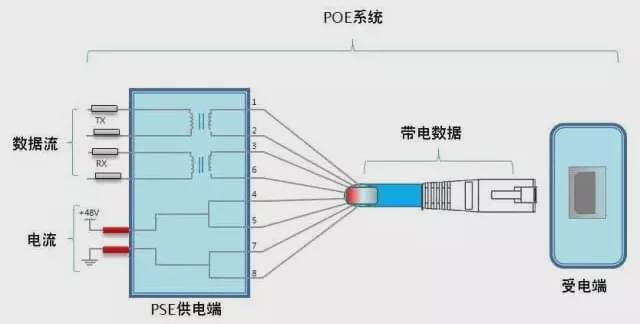

- 在建筑與數(shù)據(jù)中心層面,綜合布線系統(tǒng)指將計(jì)算機(jī)、網(wǎng)絡(luò)設(shè)備、服務(wù)器等通過標(biāo)準(zhǔn)化的線纜(如光纖、雙絞線)、連接器和配線架連接起來,形成一個(gè)模塊化、靈活性高的信息傳輸通道。這包括工作區(qū)子系統(tǒng)、水平干線子系統(tǒng)、管理間子系統(tǒng)、垂直干線子系統(tǒng)、設(shè)備間子系統(tǒng)和建筑群子系統(tǒng)六個(gè)部分的規(guī)劃與實(shí)施,是信息系統(tǒng)高效、穩(wěn)定運(yùn)行的“神經(jīng)網(wǎng)絡(luò)”。

六、 結(jié)論:協(xié)同精密的工程金字塔

納米集成電路的制造與計(jì)算機(jī)系統(tǒng)集成,構(gòu)成了一個(gè)從微觀原子尺度到宏觀設(shè)備尺度的完整技術(shù)金字塔。底層的CMOS與存儲(chǔ)器制造工藝,以納米級(jí)的精度雕刻出信息時(shí)代的基石;上層的系統(tǒng)集成與綜合布線,則以系統(tǒng)工程的思維,將這些基石穩(wěn)固、高效地連接起來,構(gòu)建出強(qiáng)大的信息處理能力。兩者相輔相成,共同推動(dòng)著計(jì)算技術(shù)的不斷演進(jìn),支撐著數(shù)字世界的持續(xù)繁榮。隨著異構(gòu)集成、光電融合、量子計(jì)算等新范式的發(fā)展,這一金字塔的結(jié)構(gòu)將變得更加復(fù)雜和精妙。